无论你是否是专业领域的从业人员,近期都一定关注到了芯片,以及围绕芯片的相关话题。比如从各种途径了解到了制造高性能的芯片是多么的复杂与困难,知道了荷兰的阿斯麦尔,知道了光刻机,但这只是皮毛。

如果将时间维度放大就会发现,一枚芯片,或集成度极高的半导体产品的产出不仅需要先进的原材料及制造设备,设计、工艺、封装测试同样决定了产品的最终性能。

在芯片设计领域,面对愈发复杂的电路结构,电子设计自动化工具(EDA)的作用也愈发凸显,就目前的国内市场而言,主流EDA工具包括来自美国的Synopsys和Cadence、来自德国的Mentor,来自我国华大九天集团的Empyrean以及新兴科技企业奇捷科技的EasyECO。

奇捷科技于2014年在香港成立,初创团队包括香港中文大学计算机科学与工程系教授与多名博士毕业生,目前已经推出了可以自动处理Functional ECO问题的EDA工具 EasyECO。Functional ECO是EDA设计流程流程后期的一个步骤,可以通过后期局部的逻辑补丁将前期错误的逻辑功能进行修正或增加逻辑功能。

在芯片的整个设计过程中,前期的逻辑电路的搭建往往自动化程度较高,但在后期的逻辑修正阶段,目前我国大部分企业仍然在采用工程师手工排查修正的方法。奇捷科技创始人兼首席技术官魏星本科毕业于北京清华大学计算机科学与技术系,研究生阶段同样攻读于清华大学EDA实验室,毕业后加入香港中文大学EDA实验室并取得博士学位。

他对创业邦说:“目前市面上的绝大多处公司依然在采用手工修正的方法,这个比例可达90%甚至更高,只有极少数大型企业使用了自动化工具软件进行修正。”这一方面是因为我国芯片产业起步不久,相关设计的复杂度和工艺还不够先进,另一方面是由于市面上的国外ECO工具价格昂贵,存在一定的垄断情况。

随着芯片性能的发展,其电路结构复杂程度也成指数级提升,手工修正的方式受到了明显的规模限制。在一些设计较为简单的逻辑电路中,工程师还可以通过数天的时间较好地完成逻辑修正任务,但在28纳米以下,比如10纳米、7纳米甚至5纳米级的芯片逻辑电路中,其复杂程度已经超过了人工修正的能力范围。

同时,人工修正的效果完全取决于工程师的经验及技术水平,不仅修正时间和成果不可控,对企业来说也加大了对人员的依赖,此外激烈的市场竞争和较短的研发周期也在迫使企业提升自身的运行效率。

奇捷科技的ECO工具EasyECO可以在Premask、Postmask等多个阶段进行逻辑修正操作,并且已经支持 7纳米的最先进工艺,在逻辑修正过程中还会同时考虑扫描链、时钟树等因素,以保证得到最好的修正结果。就使用效果而言,奇捷科技EasyECO可以通过修改更少的逻辑点来实现最终的修正结果,而更少的修正点就意味着更快的修正速度,同时也不会影响芯片最终的性能和尺寸。

奇捷科技的原创算法是其产品高性能的基石。

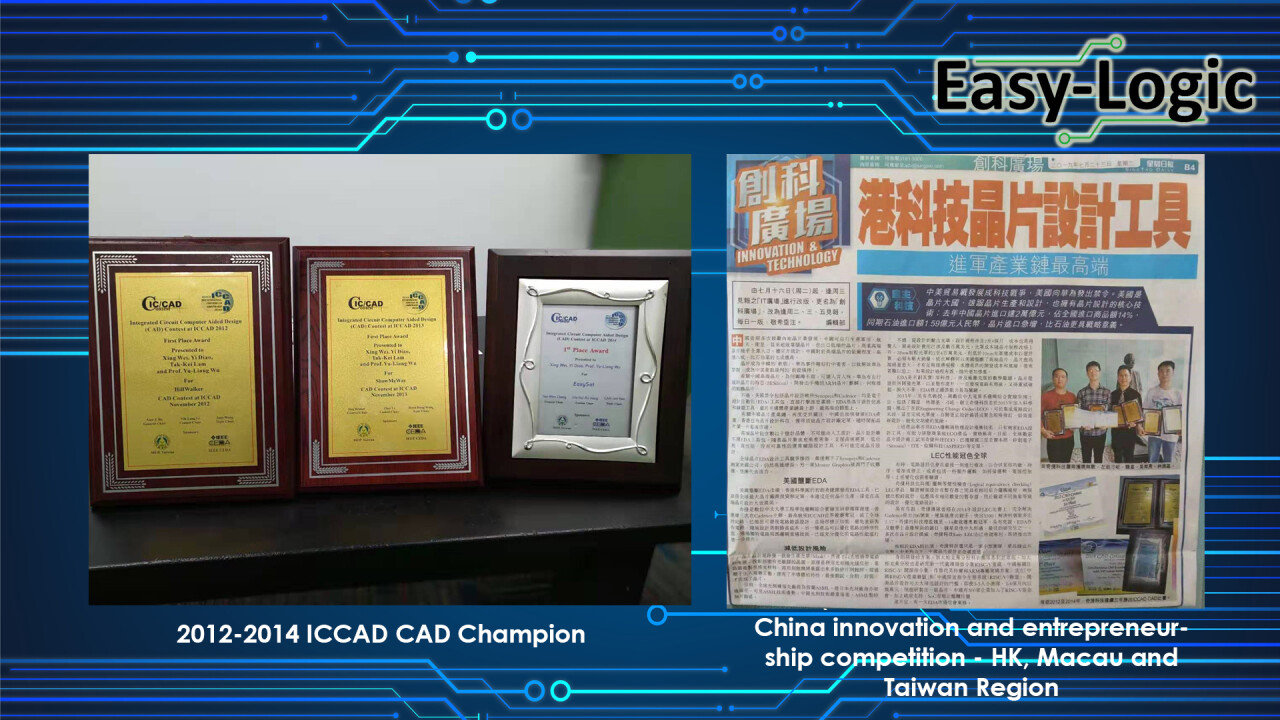

2014年,奇捷科技的算术逻辑形式验证技术在ICCAD举办的国际CAD竞赛中获得了LEC题目的冠军,其与目前主流的国外EDA工具相比性能也具有较大优势,这几乎是一种革命性的技术革新。

在此后的商品化进程中,奇捷科技也经历了支持电路读取、标准单元库识别等一系列阶段,魏星对创业邦说:“我们的核心算法体量很小,但我们依然编写了数十万行代码用于算法的实际应用,才使其真正成为了满足工业化标准的工具,这个过程是十分艰难的。”

目前奇捷科技拥有十余名员工,产品用户主要集中在台湾和韩国,客户通过支付年费来使用EasyECO,并享受后续的升级更新服务。据了解奇捷科技目前已经产生了一定规模的营业额,并计划逐步进入大陆市场和美国市场,利用全球化的战略布局扩大其拥有的市场先发优势。

融资方面,奇捷科技于2016年12月获得了国内知名半导体基金投资的60万美元天使轮融资,2019年四月获得了国际知名半导体设计公司投资的200万美元A轮融资,魏星表示新一轮的融资计划也已经启动。

本文文章图片来源于奇捷科技,经授权使用。本文为创业邦原创,未经授权不得转载,否则创业邦将保留向其追究法律责任的权利。如需转载或有任何疑问,请联系editor@cyzone.cn。